## Dualzähler

Die rechteckförmigen Zählimpulse werden als Taktsignale **C** („clock“) demjenigen JK-Flip-Flop zugeführt, welches das LSB (least significant Bit,  $2^0$ ) der Dualzahl repräsentiert. Das Signal am Ausgang **Q** eines jeden Flip-Flops wird als Taktsignal dem Flip-Flop für das jeweils nächst höherwertige Bit eingespeist.

Der Dualzähler ermittelt die Anzahl der Rechteckimpulse.

### Merke:

Falls die Flip-Flops jeweils auf der fallenden Taktflanke triggern, liegen die die Dualzahl definierenden Bits am jeweiligen Ausgang **Q** an. Triggern die Flip-Flops jeweils auf der steigenden Taktflanke, liegen die die Dualzahl definierenden Bits am jeweiligen Ausgang  $\bar{Q}$  an.

Für einen Dualzähler mit Zählbereich **0 . . .  $2^n - 1$**  benötigt man **n** Flip-Flops, mit denen der Zähler  $2^n$  Zustände annehmen kann. Jedes dieser Flip-Flops repräsentiert eine Ziffer der Dualzahl.

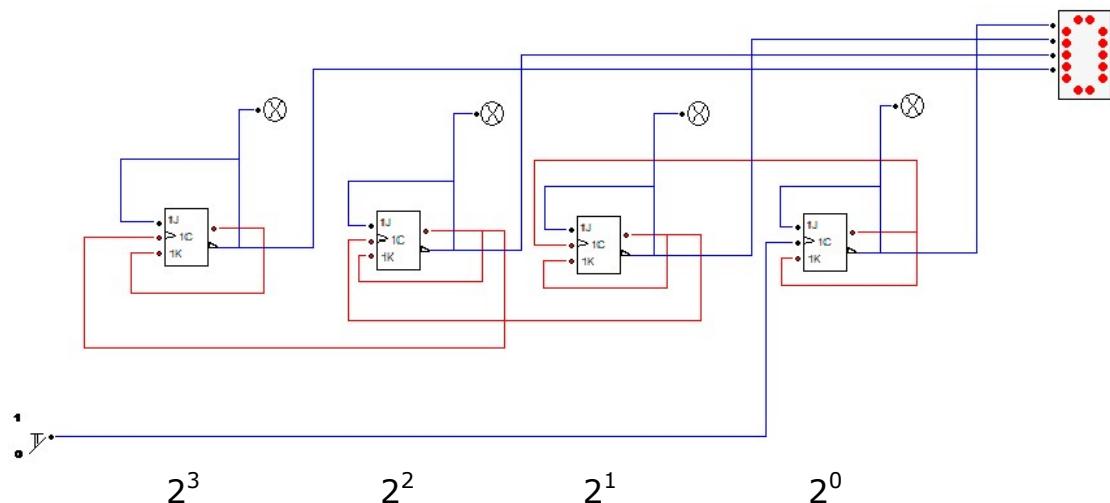

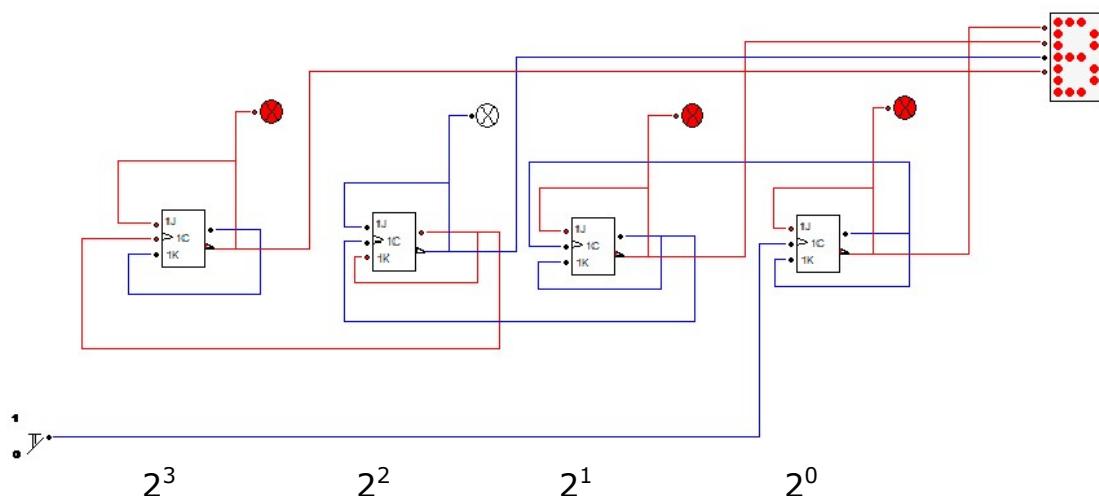

### 4-Bit-Dualzähler mit Triggerung auf der steigenden Taktflanke

Die Betätigung des Tasters erzeugt jeweils ein rechteckförmiges Taktsignal.

Anfangszustand:

Zustand nach 11-maligem Betätigen des Tasters:

$$B_{\text{HEX}} = 11_{\text{DEC}} = 1 \cdot 2^3 + 0 \cdot 2^2 + 1 \cdot 2^1 + 1 \cdot 2^0 = 1011_{\text{DUAL}}$$

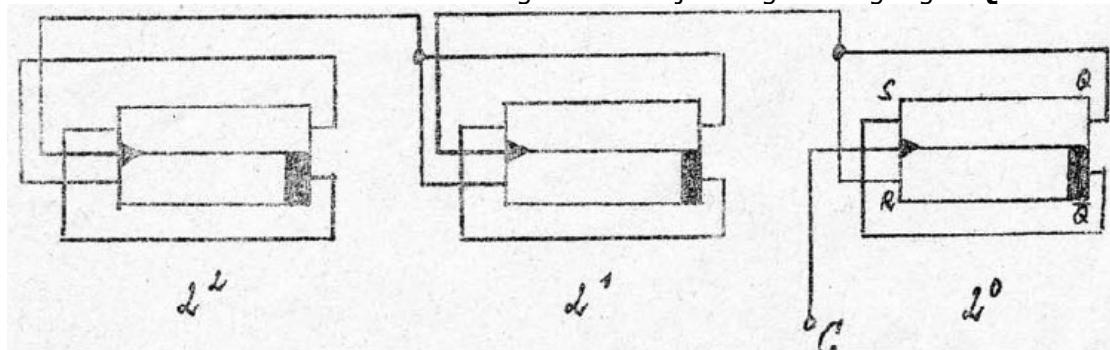

### 3-Bit-Dualzähler mit Triggerung auf der fallenden Taktflanke

Die zu zählenden Rechteckimpulse werden dem Takteingang **C** des für das LSB zuständigen Flip-Flops zugeführt.

Die die Dualzahl definierenden Bits liegen an den jeweiligen Ausgängen **Q** an.

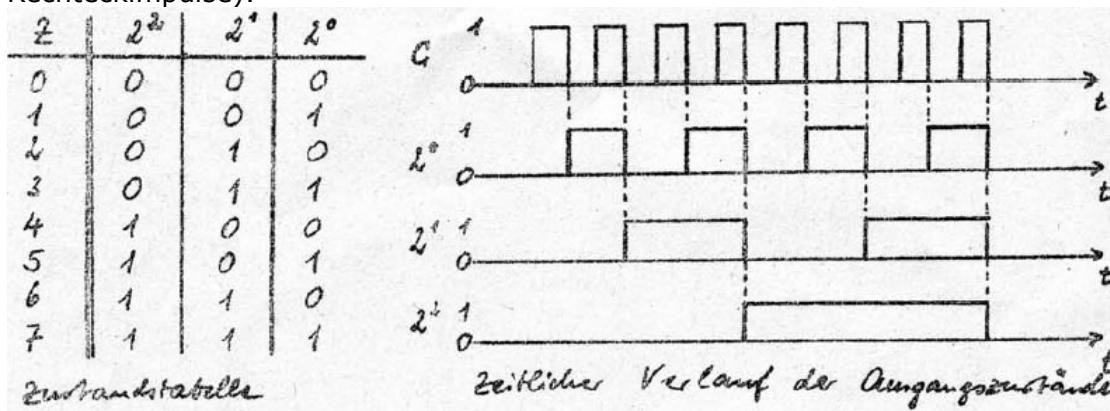

Timing bei einem 3-Bit-Dualzähler ( $z$  = Anzahl der bei **C** eingespeisten Rechteckimpulse):

für einen Dualzähler mit Zählbereich  $0 \dots 2^z - 1$  benötigt man  $z$  FLIP-FLOPs ( $2^z$  Zustände).

**Hinweis:** Wie man obenstehenden Zeitdiagrammen entnimmt, wird das Flip-Flop für die Stelle  $2^1$  mit der halben Frequenz desjenigen Signals getaktet, welches am Takteingang **C** des Flip-Flops für die Stelle  $2^0$  anliegt. Somit lässt sich mit dieser Schaltung eine gegebene Taktfrequenz (z. B. diejenige einer CPU) zeitsynchron halbieren (vierteln, achteln, ...).

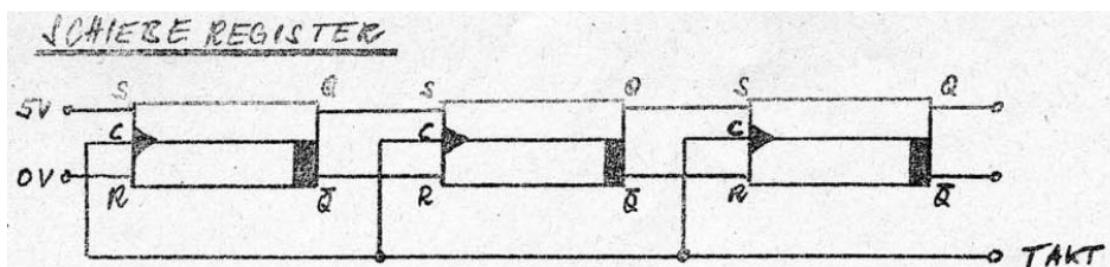

### Anhang: 3-Bit-Schieberegister

Beispiel:

|                                       |   |   |   |

|---------------------------------------|---|---|---|

| vor der ersten fallenden Taktflanke   | 1 | 0 | 1 |

| nach der ersten fallenden Taktflanke  | 0 | 1 | 0 |

| nach der zweiten fallenden Taktflanke | 0 | 0 | 1 |

| nach der dritten fallenden Taktflanke | 0 | 0 | 0 |

Die zu Beginn im Register stehende Information (hier: 3-bit-Information) ist nach dem 3. Takt völlig aus dem Schieberegister "ausgeschoben" worden.