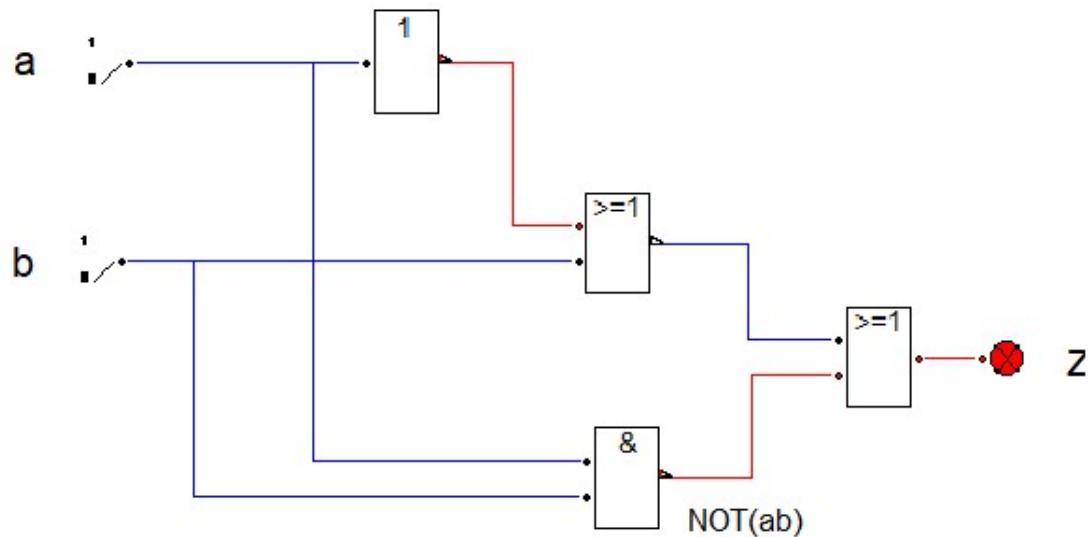

3. Gegeben ist folgende digitale Schaltung mit den Eingangsvariablen  $a$ ,  $b$  und der Ausgangsvariablen  $z$ :

- a) Ermittle den Booleschen Term für die Boolesche Funktion  $z = f(a, b, c)$ .

Hinweis: Notiere am Ausgang jedes Gatters jeweils den Booleschen Term (Beispiel:  $\overline{a} \cdot b$  am Ausgang des NAND-Gatters).

- b) Vereinfache den in a) erhaltenen Term unter Verwendung der Rechenregeln für Boolesche Ausdrücke; erstelle die Wahrheitstafel.

- c) Zeichne das Schaltbild für den vereinfachten Funktionsterm und teste beide Schaltungsvarianten mit einem Digitalsimulator.

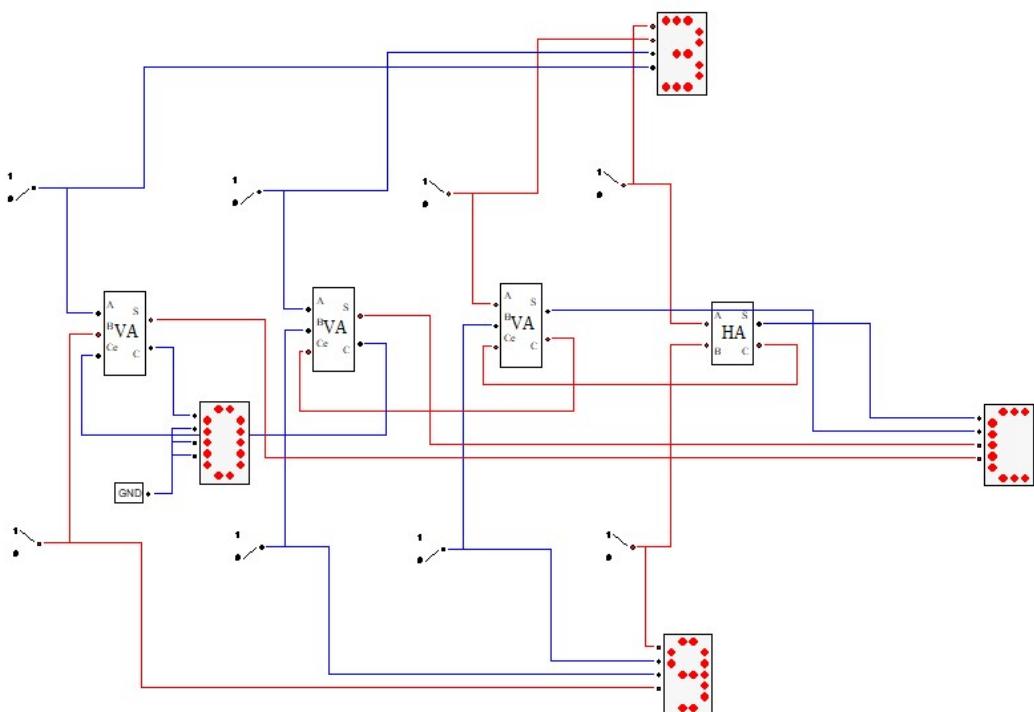

4. 4-Bit-Paralleladdierer mit Anzeige der Summanden und der Summe jeweils im Hexadezimalformat

Erweitere die Schaltung „4-bit-Paralleladdierer.dsim“ (auf [www.kalle2000.de](http://www.kalle2000.de) downloadbar) zu einem 8-Bit-Addierer mit numerischer Anzeige.